由 PCI-SIG® 开发的 PCI Express®(PCIe®)高速串行计算机扩展总线标准目前已经在数据中心, 人工智能/机器学习,HPC,车载,IoT,航空以及航天应用中。自从 PCIe 5.0 和 6.0 分别于 2019 年和 2022 年发布以来,PCIe 在现代主板和固态硬盘中变得更加普遍。PCIe 设计也自然而然变得千姿白态。让我们来了解 PCIe 设计及测试的关键考量因素,以优化您的测试流程。

简介 PCIe 标准

为 2.5 GT/s 速度的 PCIe 1.0 于 2003 年首次推出,而预计在 2025 年发布的 PCIe 7.0 将具备惊人的 128 GT/s 速度。这发展也限时了 PCI-SIG 在推动数据传输速度发展上的承诺。从 PCIe 2.0 的 8b/10b 编码到 3.0 128/132 编码,以及 PAM4(脉冲幅度调制 4)的引入,显示了该技术的持续进步。这些更新使得 PCI-SIG 平均每三年发布一次新版本,数据传输速度翻倍。

图 1: PCIe 科技的进化

PCIe 最新的三迭代(4.0,5.0,6.0)

如果把过去三次 PCIe 迭代做一个比较,会发现 PCIe 4.0 和 5.0 的奈奎斯特频率(Nyquist Frequency)翻了一番,而 PCIe 6.0 则保持不变。不过,通过不同的调制方案,PCIe 6.0 的数据传输速率还是提高了一倍。插入损耗通道在 PCIe 4.0 到 5.0 之间也有所增加,而在 PCIe 6.0 中则有所减少。这也被认可为数据速率翻倍的有益权衡。

参考 CTLE 和 DFE 在所有迭代中也都有所增加,以适应更高的插入损耗或噪声。此外,PCIe 4.0 中校准接收器眼和测试的最小范围带宽要求也提高到 25GHz。在 PCIe 5.0 中,传输器和接收器测试的阈值提高到 33GHz,但同一标准的接收器校准和链路均衡设置需要 50GHz。在 PCIe 6.0 中,校准和测试都必须使用 50GHz。

了解 PCIe 的3中层面

图 2: PCIe 的3层

首先,让我们了解 PCIe 三层核心硬件所办的角色:

- 交易层 (TL): TL 位于堆栈顶部,通过实施事务流控制机制和管理数据包在链路中的传输来协调数据的传输和接收。

- 数据连接层 (DLL): 中位于在上层 TL 和 下方物理层(PHY)之前是 DLL。它负责管理数据成帧、错误检测和流量控制,同时促进端点之间的通信。

- 物理层 (PHY): 该底层由差分对和时钟分配机制等元素组成,可促进数据交换。它管理 PCIe 链路的电气特性,包括信号传输和接收。

负责驱动程序和配置任务的软件层和操作系统层则设在TL、DLL 和 PHY 这三个核心层之上。虽然软件层和操作系统层也负责 PCIe 设备的整体功能,但它们并不被视为 PCIe 的一部分,而通常是在软件架构以及设备管理等非 PCIe 协议本身的前提下被讨论。

PCIe 物质层

图 3: PCIe 物质层

在物理层,单线的 PCIe 链路中由两条独特连接差分对组成点对点连接,二这两条链接通过嵌入式时钟支持同步。该架构支持 SRIS 和 SRNS 时钟方案,助于实现稳健的通信。此外,PCIe 允许各种通道宽度,包括 x1、x2、x4、x8、x12、x16 和 x32,从而满足不同的互连要求。

图 4: PCIe 4.0, 5.0, 6.0 规范

PCIe Base vs CEM 规范

PCIe 中的两个主要规范是 Base 和 CEM。两中规范在测试点定义,方法和正式程度上有很大的区别。- Base 规范: 定义芯片级的电气一致性,包含架构、协议、链路层、物理层和软件接口的技术细节。没有官方的符合性程序或测试夹具。

- CEM (Card Electromechanical) 规范: 定义了完整产品的机械要求和电气合规性,即组件(端点、桥接器/交换机、根复合体)、附加卡或系统(又称 “Host”)。测试夹具和测试工具由 PCI-SIG 明确定义和提供。测试和符合性由《符合性测试规范》(CTS)规定。

遵循 Base 规范或 CEM 规范的选择取决于您的产品性质和客户。芯片制造商主要遵循 Base 规范,侧重于硅级测试和验证。终端产品制造商遵循 CEM 规范,确保符合 PCIe 连接器标准。除基本规范和 CEM 规范外,还有针对外形尺寸的子规范。

PCIe 合规计划

PCIe 合规性计划负责监督 PCIe 产品的认证,确保符合严格的 PCI-SIG 标准。产品必须通过 PCI-SIG 研讨班或授权测试实验室的测试才能获得认证,并在成功通过所有 Gold Suite 测试且互操作性测试通过率达到 80% 后,才会被列入 PCI-SIG 集成商名单。目前,合规计划仅适用于 PCIe 4.0 和 5.0 产品,官方集成商列表认证测试仅支持 CEM 外形。如果您希望测试其他形式因素,则需要携带合适的适配器,以便在测试期间将其转换为 CEM。

各种产品类型所需要的测试包括:图 5: 各种产品类型的测试

概观 PCIe CEM 规范的传输器测试

PCIe 传输器测试专注于验证各种数据速率的信号完整性和质量。

要测试的通道取决于系统的配置。8、16 和 32 GT/s 的所有发射机预置都必须在通道 0 上进行测试,这是 PCIe 链路中用于通信和配置的主要通道。信号质量和抖动测试也在 0 通道上进行,如果存在相邻通道(N-1),则使用一个合格预置进行测试。大于 x4 的配置需要对 0、N-1 和 N/2-1 通道进行测试。合格预设可确保发射机在测试期间对所有车道的配置保持一致,从而准确比较和评估各车道的信号质量。

例如,

- x1 配置的测试将在车道 0 上进行

- x2 配置的测试将在车道 0 和 1 上进行

- x4 配置的测试将在车道 0 和 3 上进行

- x16 配置的测试将在车道 0,15 和 7 上进行

RefCLK 仅对 32 GT/s 系统进行单独测试。对于所有较低的数据速率,RefCLK 都是在测试发射机信号质量时间接测试的。因此,对于 16 GT/s 或更低的速度,需要使用四通道示波器(也称为双电压测试配置)进行全面测试。

PLL 峰值和带宽仅在通道 0 上使用脉冲宽度抖动 (PWJ) 和/或 P7 兼容模式进行测试。图 6: 为 PCIe CEM 传输器测试的必要官方 PCI-SIG 测试装置

Watch 收看研讨会的完整重播,了解 PCIe CEM 装置表征以及 PCIe 5.0 CEM 规范传输器测试

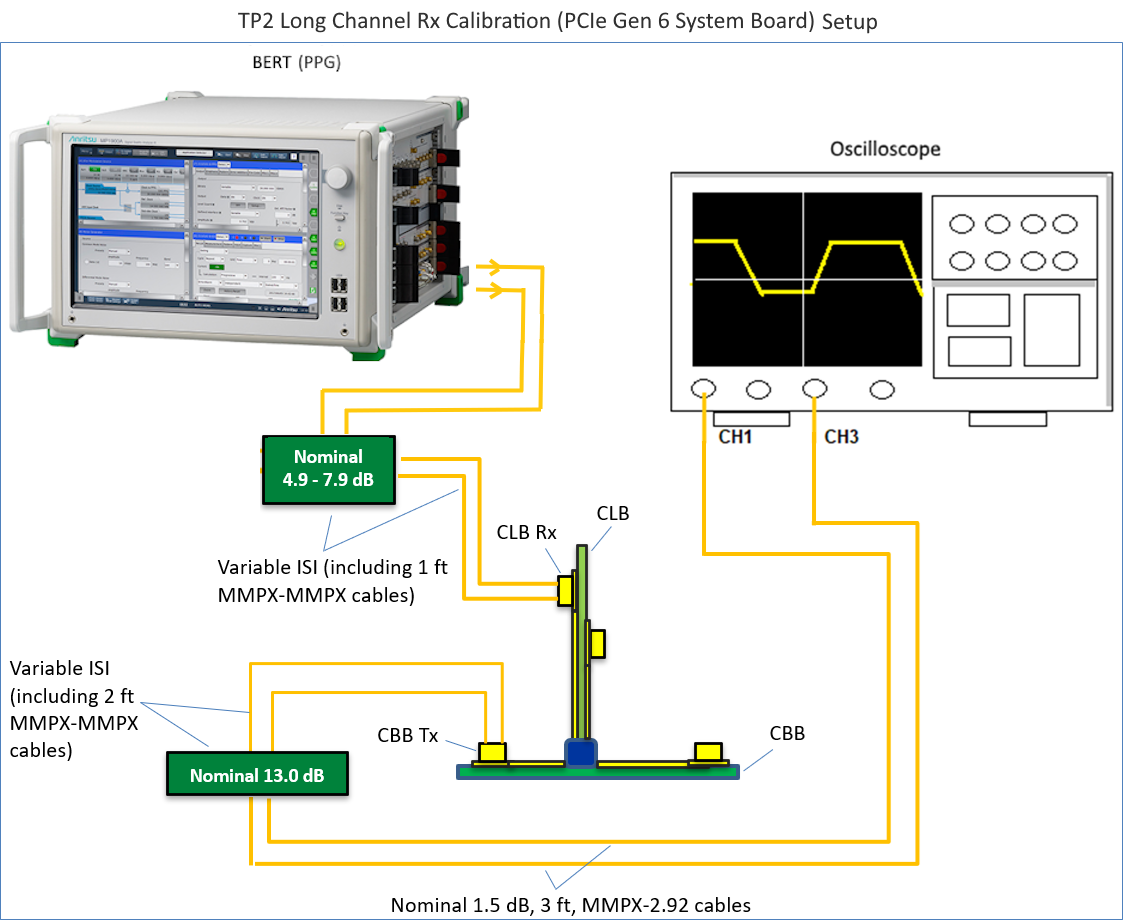

接收器链路均衡(Link EQ)测试的目的是保证受测的接收器在零比特2误差的情况下能够达到 1E-12 比特误码率(BER)。PCIe 接收机链路均衡测试程序如下:- 步骤一:根据所需的数据速率对应力眼进行校准 (图 7)

- VNA 的通道损耗

- 眼振幅、预设、SJ 和 RJ,由 BERT 和 RTO 设置

- 通过 BERT 和 RTO 检测 DM-I 和眼高/眼宽

- 步骤二:连接培训

- 通过恢复状态的 BERT 使 DUT进入环回模式

- 排查故障

- 步骤三:误码率的测量达到 95% 的置信水平

- 使用 Stressed EYE 检查 BER <1E-12(强制)

- 抖动容限测试(可选)

图 7: PCIe 接收器链路均衡测试校准期间 PCIe 4.0 和 PCIe 5.0 的最小和最大眼高和眼宽要求

PCIe 链路层和交易层测试

除物理层外,PCIe 测试还扩展到链路层和事务层,以解决错误处理和协议合规性问题。链路层和事务层测试的主要目标是从逻辑物理层开始,逐层验证错误处理。这些测试旨在验证功能的实现并确保其正常运行。

链路层和交易层的测试包括:

- 链路层测试

- 交易层测试

- 逻辑 PHY 层测试(均衡协议)

- 逻辑 PHY 层测试(训练序列中的保留位)

- 车道边线测试 – 功能测试

电气 PHY 层测量设备的模拟特性,以确保正确的信号传输和接收,而逻辑 PHY 层指的是物理层中用于调整电信号的协议,实际上是一种协议机制。因此,上述逻辑 PHY 层测试使用协议测试工具而非电气测试工具进行。

PCIe 链路层测试

PCIe 的链路层测试侧重于评估各种机制,以确保 PCIe 链路上的数据传输和恢复正常。这些测试可确保链路在指定参数范围内运行,包括数据速率、错误检测和纠错机制。

通常在链路层测试的机制包括:

- 重播计时器/重播编号/NAK 时重播

- 不良数据链路层数据包 (DLLP)

- 重放计数器

- 坏链路循环冗余码 (LCRC)

下表中有更多链路层测试的示例。这些测试使用协议测试卡(PTC)或练习卡进行。

图 8: PCIe 链路层测试例表

PCIe 交易层测试

事务层测试包括检查事务层数据包(TLP)传输中的错误。这些测试包括 TLP 中的错误信息等情况,确保请求完成。检测中毒 TLP、错误 TLP 序列号和无效 TLP 的测试是 PCIe 合规性测试的必测项目,而不良端点循环冗余检查 (ECRC) 检测则是可选项目。

图 9: PCIe 交易层测试例表

PCIe 均衡测试 (3.0 或更高)

当 PCIe 链路中的所有连接设备都能支持 PCIe 3.0 或更高的数据传输速率时,就会进行链路均衡以优化连接,并以更高的数据传输速率建立最稳定的 PCIe 链路。因此,从 PCIe 3.0 开始,必须针对设备支持的所有数据速率进行均衡测试。

- 调整预设,确保训练序列中的反应正确无误

- 根据设备的全摆幅 (FS) 和低频 (LF) 信息,运行 55 种不同的系数组合

图 10: PCIe 均衡测试例表

收看研讨会重播,了解 PCIe 5.0 和 6.0 的差别等详情

PCIe 划线测试(适用于 4.0 及以后的版本)

Lane margining 是一种软件机制,在 PCIe 4.0 中作为可选测试引入,不影响纳入集成商列表。不过,从 PCIe 5.0 开始,它已成为强制性测试项目。 Lane margining 要求在接收器内的不同采样点执行不同的步骤,以确保正确实施。当主机向终端请求保证金信息时,通过检查返回的数字及其与保证金的关系进行验证。 虽然电子(物理层)测试规范中定义了车道边沿测试,但它是以三种不同的方式与链路和交易测试一起运行的:- 插件卡 – 无需设备驱动程序

- 插件卡 – 需要设备驱动程序

- 系统车道边距测试

在系统线路余量测试中,端点的电气特性会发生变化,系统报告的余量也会随之测量。如果系统中存在重定时器或交换机,则测试需要测量与插槽或交换机下游端口相连的下游重定时器端口。

让您的 PCIe 设计在 GRL 实验室经受专业的考验

作为获得 PCI-SIG®批准的首家 PCIe 授权测试实验室,GRL 专家能帮您顺利符合从1.0 到 6.0 的 PCIe 规范。欢迎您随时联系我们,开始您的合规之旅。

若想了解解决方案的更多详情,您可以点击此处观看研讨会的重播。