Granite River Labs, GRL

曾威华 Wing Tseng

本篇文章我们将介绍USB3.2的物理层(Physical Layer)测试。在物理层测试当中,分为传送(Transmitter)测试以及接收(Receiver)测试两大部分,传送测试可比喻成验证USB产品的说话能力,接收测试则比喻为USB产品的听力。通过测试认证的USB产品就应当有着稳定的讯号传送及接收能力。USB3.2在开始传输信息之前,会先使用LFPS讯号先行沟通,这种低频周期讯号可节省产品功耗,所以在物理层的讯号测试也会对LFPS讯号进行测试。

数据包类型分为四种:

- Link Management Packet (LMP)

- Transaction Packet (TP)

- Data Packet (DP)

- Isochronous Timestamp Packet (ITP)

通常在物理层测试之后,接着需要测试USB的链路层,本篇文章我们将来介绍USB3.2 Link Layer测试项目。

USB3.2 Link Training and Status State Machine(LTSSM)

在进入我们的链路层测试介绍中,我们先认识USB3.2的LTSSM,LTSSM是USB3.2在讯号沟通之后可能的链路状态流程图,USB3.2 LTSSM如图(一) 。

图 (一) 来源 : Universal Serial Bus 3.2 Specification

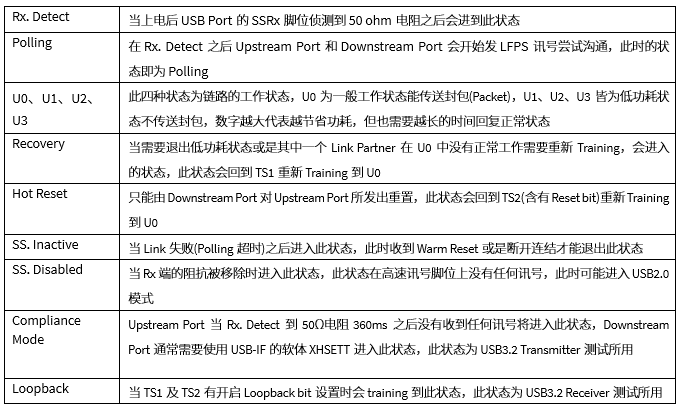

表(一)为LTSSM的各种状态介绍:

表(一)

USB3.2 Polling Substate Machine

有了LTSSM的认识之后,换介绍USB3.2 Polling子状态,图(二)为Polling Substate Machine可从图中了解到USB3.2 Gen2的Polling沟通讯号顺序为:

SCD1 → SCD2 → LBPM PHY Capability → LBPM PHY Ready → TSEQ → TS1 → TS2

另外也讲述USB3.2 Gen1的Polling沟通讯号顺序为:

LFPS → TSEQ → TS1 → TS2

所以我们发现SCD1及SCD2和LBPM系列是USB3.2 Gen2才新增的一种LFPS沟通讯号。举例来说,对照图(二)可知道当Link Partner沟通SCD2完毕,Polling Substate会进入Polling.PortMatch状态,其他依此类推。

图(二) 来源 : Universal Serial Bus 3.2 Specification

USB 3.2 链路层测试(Link Layer Test)

有了上面的认识之后,我们可以开始介绍Link Layer测试。在测试项目中分有TD6.X和TD7.X部分,两者皆属于USB的链路层测试部分,TD6.X的测项较偏物理层的延伸测试,TD7.X属于链路层测试。以下我们将逐一介绍每一个测试项目,其中Link Validation System(LVS)指链路验证系统,目前常作为LVS测试仪器为LeCroy的M310P。

TD6.1 Lane Polarity Inversion Test

LVS将SSTx+及SSTx-做一个颠倒反向去与PUT进行沟通,PUT能够顺利沟通进入到U0即为Pass, Port Under Test(PUT)则是指待测Port。

TD6.2 SKP Test

此测项是测PUT能够支持所有可能遇到的SKP组合,且能够顺利training进入U0并维持50ms。

SKP为Skip Ordered Set其来由是因为在USB3.2的高速传输下规范必须要有SSC展频频率,Link Partner在SSC的关系下会造成双方的传输与接收的Data Rate不一致,所以需要使用SKP来补足Link Partner因SSC造成的空档时间。

测试方式为LVS在LFPS沟通之后到U0之前,会在TS1以及TS2结尾部分塞入SKP,塞入规则Gen1和Gen2不同,以下分别列出:

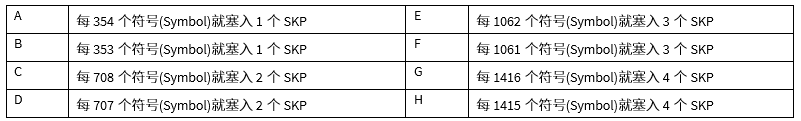

对Gen1的PUT有八组测试如表(二)

表(二)

对Gen2的PUT有四组测试如表(三)

表(三)

若PUT没有Re-Timer,X = {4, 8, 12, 16, 20, 24, 28, 32, 36}

若PUT有Re-Timer,X = {8, 12, 16, 20, 24, 28, 32}

例如下图(三)为Gen1的第C组测试Trace,可看见LVS在TS1和TS2的部分依照规则塞入SKP,然后成功和PUT沟通进入U0维持50ms,所以此测项为Pass。

图(三)

TD6.3 Elasticity Buffer Test

此为PUT的传输速度缓冲测试,LVS会模拟-5300ppm以及300ppm的SSC讯号与PUT沟通,PUT能够顺利进入U0即为Pass。

TD6.4 LFPS Frequency Test

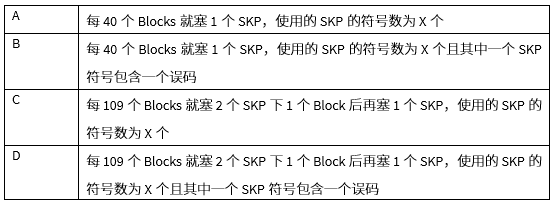

在USB3.2中,开始传输数据之前会先使用LFPS来与Link Partner沟通,所以需要测试LFPS在规范范围内的不同频率下是否还能顺利的沟通下去。LFPS频率测试分为两组如表(四):

表(四)

首先LVS第1组用频率Min LFPS(10MHz)测试,第2组LVS则用频率Max(50MHz) LFPS去做测试。PUT要能够在两组不同频率的LFPS顺利沟通进到Polling.RxEQ子状态即为Pass。

提供以下表(五)为LFPS的规范tPeriod范围,即可明白为何此测项定义的Max频率以及Min频率是这个数字。

表(五) 来源 : Universal Serial Bus 3.2 Specification

图(四)举例Pass的第1组测试,第1个红框为PUT与LVS沟通发送的LFPS,接下来LVS用Min LFPS(10MHz)回PUT,第2个红框看见PUT仍然有LFPS回LVS,第3个红框表示PUT和LVS顺利沟通进入Polling.RxEQ

图(四)

TD6.5 Polling.LFPS Duration Test

在TD6.5测试LVS用Polling.LFPS在规范范围内的Max与Min的tBurst和tRepeat与PUT沟通要能够顺利进入Polling.RxEQ。此测项分有四组测试整理如表(六):

表(六)

测试值一样可以从USB3.2的Polling.LFPS规范如下表(七)之中得到

表(七) 来源 : Universal Serial Bus 3.2 Specification

TD6.6 SCD Duration Test (Gen2 Capable Only)

USB3.2 Gen2的LFPS使用SCD1及SCD2来沟通,与Gen1的差别只在于tRepeat的时间长短被改变了,SCD的规范如表(八)。SCD1定义为逻辑上的“0010”,SCD2则定义为逻辑上的“1101”

表(八) 来源 : Universal Serial Bus 3.2 Specification

接下来就用一样的原理,LVS使用在规范内Max与Min数值的SCD讯号与PUT沟通,然后能够顺利进入到Polling.PortMatch即为Pass,LVS测试使用八组如表(九):

表(九)

TD6.7 PWM Duration Test (Gen2 Capable Only)

USB3.2在SCD讯号沟通完之后会换使用LBPM来沟通,LBPM是LFPS去做脉冲长度调变的一种讯号,LBPM的规范如表(十):

表(十) 来源 : Universal Serial Bus 3.2 Specification

使用同TD6.6的原理,LVS用Max与Min数值的LBPM去跟PUT沟通要能够顺利进入Polling.RxEQ即为Pass,LVS测试使用八个组合如表(十一):

表(十一)

TD7.1 Link Bring-up Test

此测项要确保PUT与LVS的沟通能够顺利进到U0且沟通的讯号数量也都符合规范。其中又分为五个子测项,若为Gen1的PUT要测子测项1及2,有Gen2的PUT要再多测子测项的3、4和5。

子测项1 : TD7.1.1模拟Gen1的LVS与Gen1的PUT沟通

- LVS等待PUT的Polling.LFPS

- LVS收到之后发送4个Polling.LFPS

- PUT没有Re-timer至少连续发送16个Polling.LFPS;若有Re-Timer至少连续发送4个Polling.LFPS。当PUT收到1个Polling.LFPS时,至少要连续发送4个Polling.LFPS但不可超过6

- 接着开始TSEQ的Training,LVS会发65536个TSEQ,PUT也要回TSEQ但中间不可包含SKP和Idle符号以及任何封包、符号和Ordered Set

- 然后是TS1 Training,LVS等待连续8个的TS1或TS2,在TS1指令集传送的中途不可有SKP打断

- 进入TS2 Training,PUT收到1个TS2之后连续回传16个TS2,在TS2指令集传送的中途不可有SKP打断

- PUT和LVS双方进入U0

子测项2 :TD7.1.2 模拟Gen2的LVS与Gen1的PUT沟通

- LVS发送SCD1

- 没有Re-Timer的PUT要连续发送至少16个Polling.LFPS

- LVS发送4个SCD1及收到16个Polling.LFPS之后要改为发送Polling.LFPS

- 接着PUT要连续发送至少4个Polling.LFPS但不可超过6个

- 接续TD7.1.1的第4步骤

子测项3 :TD7.1.3模拟Gen1的LVS与Gen2的PUT沟通

- LVS发送16个Polling.LFPS

- PUT在收到LVS的16个Polling.LFPS及发送4个SCD1之后改发Polling.LFPS

- 没有Re-Timer的PUT要发送16个Polling.LFPS

- 在收到LVS的1个Polling.LFPS后,PUT要连续发送4个Polling.LFPS

- PUT没有Re-Timer发送16个Polling.LFPS之后要进Polling.RxEQ;若有Re-Timer则是发送4个Polling.LFPS之后要进Polling.RxEQ

- 接续TD7.1.1的第4步骤

子测项4:TD7.1.4模拟Gen2的LVS与Gen2的PUT沟通

- LVS发送SCD1

- PUT在收到1个SCD1或SCD2之后发送2个SCD1

- LVS在发送2个SCD1及收到1个SCD1或SCD2之后发送SCD2

- PUT在收到1个SCD2之后发送2个SCD2

- PUT在收到2个连续PHY Capability或PHY Ready之后发送3个连续PHY Capability

- LVS发送524288个TSEQ,TSEQ每16384个Ordered Sets塞入SYNC

- PUT也回送TSEQ,TSEQ每16384个Ordered Sets塞入SYNC且中间不可包含SKP和Idle符号以及任何封包、符号和Ordered Set

- LVS发送TS1,TS1每32个Ordered Sets塞入SYNC,如有需要也可加入SKP

- LVS要收到PUT的连续8个相同的TS1或TS2

- LVS连续发送8个相同的TS1或TS2之前PUT发送TS2,在TS1训练的中途不可有SKP或SYNC打断

- LVS发送TS2,TS2每32个Ordered Sets塞入SYNC,如有需要也可加入SKP

- PUT在收到1个TS2之后发送连续16个TS2,在TS2训练的中途不可有SKP或SYNC打断

- LVS发送连续8个TS2之前PUT发送Idle符号,接着LVS发送1个SDS和含有Data Blocks的Idle符号

- PUT和LVS双方进入U0

子测项5 : TD7.1.5模拟Gen1的LVS与Gen2的PUT沟通(有别于TD7.1.3这次是等待PUT先发送)

- LVS等待PUT的SCD1

- LVS发送Polling.LFPS然后进入Polling.RxEQ

- PUT要改发送Polling.LFPS降到Gen1然后进入Polling.RxEQ

- 接续TD7.1.1的第4步骤

TD7.2 Link Commands Framings Robustness Test

在Link Command中的前四组符号称为LCSTART,LCSTART由三个SLC和一个EPF所组成。在沟通上要能够容忍LCSTART有一个符号的错误,所以此测项LVS使用含有一个ERR符号的LCSTART与PUT沟通,能够进入U0维持50ms为Pass。分为四组去测试如表(十二):

表(十二)

以下图(五)为A组测试的范例,可看见红框中LVS发送了一组Link Command在LCSTART第1个符号是一个错误符号,但PUT还是能够与LVS继续沟通下去进入U0。

图(五)

TD7.3 Link Commands CRC-5 Robustness Test

Link Command Word(LCW)为2个Bytes,5个bits为CRC-5。在测试中LVS也会使用错误的CRC-5与PUT沟通。测试组合分为三组如表(十三):

表(十三)

Gen1在组合A、B及C都要Recovery重新training,但在Gen2的部分组合A及B可以容忍错误继续沟通进入U0并维持50ms,组合C则也是要Recovery重新training才算Pass。

图(六)

图(六)为Gen1的测试组合A范例,可从红框中发现LVS使用第1个CRC-5为错误来与PUT沟通,PUT也进入Recovery重新training。

TD7.4 Invalid Link Commands Test

此测项发送Link Commands其中第1个LCW与第二个LCW为不相同的指令,但皆有正确的CRC-5。LVS发送第1个LCW为LGO_U1与第二个LCW为LGO_U2,PUT不能够回复LAU或LXU给这样的Link Commands。当PUT收到两个不同的LCW要忽视这两个指令,继续training进入U0并维持50ms即为Pass。

图(七)

图(七)为此测项范例,可从红框看见LVS发送一个Unknown的Link Commands与PUT沟通,此Link Commands为图中下半部显示,第1个LCW与第二个LCW不相同。

TD7.5 Header Packet Framing Robustness Test

Header Packet前面四个Bytes称为HPSTART,HPSTART由三个SHP和一个EPF组成。在沟通上要能够容忍HPSTART有一个符号的错误,所以此测项LVS使用含有一个ERR符号的HPSTART与PUT沟通,能够进入U0维持50ms为Pass。分为四组去测试如表(十四):

表(十四)

图(八)为测试组合A的范例,第1个红框为LVS发送含有一个错误符号的HPSTART的Header Packet,第二个红框表示PUT可容忍此错误符号训练进入U0。

图(八)

TD7.6 Data Payload Packet Framing Robustness Test

Data Payload Packet(DPP)前四组符号为DPPSTART,结尾四组符号为DPPEND。DPPSTART由三个SDP及一个EPF组成,DPPEND由三个END及一个EPF组成。在沟通中可容忍一个错误符号在DPPSTART或DPPEND里进入U0维持50ms即为Pass,所以测试组合有八组如表(十五):

表(十五)

图(九)为Gen1的Downstream Port测试组合A范例,可看见第1个红框为LVS发含有一个错误符号的DP封包,接着第二个红框可知PUT容忍一个错误符号继续沟通进入U0。

图(九)

TD7.7 Rx Header Packet Retransmission Test

当PUT收到无效的Header Packet时,PUT要回送LBAD接着LVS回LRTY并重新发送正确的链路指令继续沟通到U0维持50ms为Pass。测试组合仿真出十种含有错误讯息的Header Packet来测试PUT如表(十六):

表(十六)

其中C到J为Gen1才需要测试的组合,且会将错误的符号放在两个不同位置各测试PUT一次:

- 位置2:SHP SHP SHP EPF DX.X KX.X DX.X DX.X

- 位置5:SHP SHP SHP EPF DX.X DX.X DX.X DX.X KX.X

图(十)为Downstream Port的Gen1组合A测试范例,可从Trace看见第1到第四个红框为LVS发一个含有错误CRC-16的HP,PUT回传LBAD,LVS再回传LRTY并再一次发送正确的LMP与PUT沟通,第五个红框PUT顺利沟通进入U0。

图(十)

TD7.8 Tx Header Packet Retransmission Test

此测项测试PUT在收到LVS的LBAD时,能够回送LRTY然后重新再发送一次LMP与LVS沟通进入U0维持50ms即为Pass。所以与TD7.7相比发现,TD7.7为PUT接收到LRTY的测试,TD7.8为PUT发送LRTY的测试。

图(十一)

图(十一)为Upstream Port的Gen1测试范例,第1到第三个红框为LVS故意发送LBAD给PUT,接着PUT有顺利的回传LRTY并且再次发送一个LMP与LVS沟通,第四个红框为PUT顺利沟通进入U0。

TD7.9 PENDING_HP_TIMER Deadline Test

此测项PUT要能够在PENDING_HP_TIMER超时之前回传LGOOD_N。如图(十二)为Gen1的Downstream Port范例,依红框顺序首先LVS在PENDING_HP_TIMER超时之前的200ns以内PUT要能够回传LGOOD给LVS的Port Capability LMP,接着继续沟通进入U0,要在U0维持50ms即为Pass。

图(十二)

TD7.10 CREDIT_HP_TIMER Deadline Test

此测项PUT要能够在CREDIT_HP_TIMER超时之前回传LCRD_X。图(十三)为Gen1的Downstream Port范例,可从红框得知在U0时,在CREDIT_HP_TIMER超时之前的tLinkTurnAround时间以内PUT要能够回传LCRD给LVS的Port Capability LMP,接着继续沟通进入U0,要在U0维持50ms即为Pass。

图(十三)

TD7.11 PENDING_HP_TIMER Timeout Test

在PENDING_HP_TIMER超时之后PUT要进入Recovery即为Pass。图(十四)为测试Gen1的Downstream Port范例,第1个红框开始PENDING_HP_TIMER,之后LVS发送Port Capability LMP与PUT沟通但是直到PENDING_HP_ TIMER超时都不发送LGOOD给PUT,第二个红框可看见PUT进入Recovery,表示PUT通过了此测项。

图(十四)

TD7.12 CREDIT_HP_TIMER Timeout Test

在CREDIT_HP_TIMER超时之后PUT要进入Recovery即为Pass。图(十五)为测试Gen1的Downstream Port范例,第1个红框开始CREDIT_HP_TIMER,之后LVS直到CREDIT_HP_TIMER超时都不发送LCRD_X给PUT,第二个红框可看见PUT进入Recovery,表示PUT通过了此测项。

图(十五)

TD7.13 Wrong Header Sequence Test

此测项为PUT收到一个错误的Header Sequence要进入Recovery即为Pass。图(十六)为Gen1的Downstream Port范例,可从第1个红框看见LVS发送一个错误的Header Sequence Number,第二个红框处PUT有顺利进入Recovery代表此测项为Pass。

图(十六)

TD7.14 Wrong LGOOD_N Sequence Test

此测项为PUT收到一个错误的LGOOD_N sequence要进入Recovery即为Pass。图(十七)为Gen1的Downstream Port范例,可从第1个红框看见LVS发送一个LGOOD_7,第二个红框处LVS发送一个错误顺序的LGOOD_2,PUT在第三个红框有顺利进入Recovery代表此测项为Pass。

图(十七)

TD7.15 Wrong LCRD_X Sequence Test

此测项为PUT收到一个错误的LCRD_X或LCRD1_X要进入Recovery即为Pass。图(十八)为Gen1的Downstream Port范例,可从第1个红框看见LVS发送一个LCRD_D,第二个红框处LVS发送一个错误顺序的LCRD_C,PUT在第三个红框有顺利进入Recovery代表此测项为Pass。

图(十八)

TD7.16 Link Command Missing Test (Upstream Port Only)

此测项为PUT在tU0RecoveryTimeout超时前没有收到LVS发送的LDN,PUT要进入Recovery即为Pass。图(十九)为Gen1的Upstream Port范例,从第1个红框为tU0RecoveryTimeout开始点,接着LVS都没有回LDN,在第二个红框PUT进入Recovery代表此测项为Pass。

图(十九)

TD7.17 tPortConfiguration Time Timeout Test

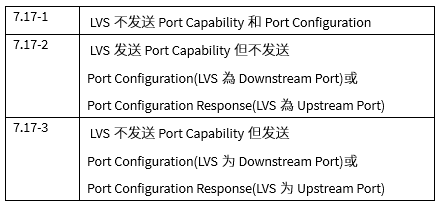

此测项若PUT为Downstream Port在tPortConfiguration超时之后要进入eSS.Inactive,若PUT为Upstream Port在tPortConfiguration超时之后要进入eSS.Disabled,规范中tPortConfiguration定为20μs。测试步骤分有三个部分如表(十七):

表(十七)

图(二十)为Gen1的Downstream Port测试TD7.17-1范例。第1个红框可看出PUT发出Port Capability,之后LVS完全不发送LMP与PUT沟通,在第二及第三个红框可知PUT在25.084μs之后进入eSS.Inactive,代表此测试Pass。

图(二十)

TD7.18 Low Power initiation for U1 Test (Downstream Port Only)

此测项为确保PUT能够进入以及退出U1状态回到U0即为Pass。图(二十一)为Gen1的范例,图中上到下左到右红框顺序为,PUT发送LGO_U1后,LVS回送LAU且PUT再回送LPMA进入U1状态,接着LVS发送U1 Exit LFPS到PUT也回送U1 Exit LFPS时间要在300ns〜2μs,PUT的U1 Exit LFPS持续发送时间要在0.9μs〜1.2μs。

图(二十一)

TD7.19 Low Power initiation for U2 Test (Downstream Port Only)

此测项为确保PUT能够进入以及退出U2状态回到U0即为Pass。图(二十二)为Gen1的范例,图中上到下左到右红框顺序为,PUT发送LGO_U2后,LVS回送LAU且PUT再回送LPMA进入U2状态,接着LVS发送U2 Exit LFPS到PUT也回送U2 Exit LFPS时间要在300ns〜2ms,PUT的U2 Exit LFPS持续发送时间要在80μs〜2ms。

图(二十二)

TD7.20 PM_LC_TIMER Deadline Test (Downstream Port Only)

此测项为测试PUT在发送LGO_U1之后PM_LC_TIMER超时前的tLinkTurnAround之内收到LVS的LAU时,PUT还能够顺利回LPMA即为Pass。图(二十三)为范例。

图(二十三)

TD7.21 PM_LC_TIMER Timeout Test (Downstream Port Only)

此测项为测试PUT在发送LGO_U1后PM_LC_TIMER超时,LVS不回送LAU给PUT,PUT要能够顺利进入Recovery即为Pass。图(二十四)为范例。

图(二十四)

TD7.22 PM_ENTRY_TIMER Timeout Test (Upstream Port Only)

此测项为测试PUT在PM_ENTRY_TIMER超时后,PUT一样可以维持在低功耗状态即为Pass。图(二十五)为范例,可看见红框中LVS发送LGO_U1,PUT回送LAU之后,LVS不回送LPMA给PUT,但PUT仍然进入U1状态。

图(二十五)

TD7.23 Accepted Power Management Transaction for U1 Test (Upstream Port Only)

此测项为PUT收到LGO_U1要进入U1,且在规范时间内的U1 Exit LFPS沟通能够Recovery回到U0即为Pass。图(二十六)为范例,LVS发送LGO_U1,PUT顺利进入U1,LVS到PUT的U1 Exit LFPS要在300ns〜2μs,PUT的U1 Exit LFPS持续发送时间要在0.9μs〜1.2μs。

图(二十六)

TD7.24 Accepted Power Management Transaction for U2 Test (Upstream Port Only)

此测项为PUT收到LGO_U2要进入U2,且在规范时间内的U2 Exit LFPS沟通能够Recovery回到U0即为Pass。图(二十七)为范例,LVS发送LGO_U2,PUT顺利进入U2,LVS到PUT的U2 Exit LFPS要在300ns〜2ms,PUT的U2 Exit LFPS持续发送时间要在80μs〜2ms。

图(二十七)

TD7.25 Accepted Power Management Transaction for U3 Test (Upstream Port Only)

此测项为PUT收到LGO_U3要进入U3,且在规范时间内的U3 Exit LFPS沟通能够Recovery回到U0即为Pass。图(二十八)为范例,LVS发送LGO_U3,PUT顺利进入U3,LVS到PUT的U3 Exit LFPS要在300ns〜10ms,PUT的U3 Exit LFPS持续发送时间要在80μs〜10ms。

图(二十八)

TD7.26 Transition to U0 from Recovery Test

此测项要确保PUT在Recovery状态时候能够回到U0即为Pass。图(二十九)为Gen1的范例,可从图中得知一开始在U0状态,LVS不发送LGOOD与PUT沟通,使PENDING_HP_TIMER超时,所以有在第二个红框进入Recovery。接着PUT与LVS要从TS1依照规范训练回到U0。

图(二十九)

TD7.27 Hot Reset Detection in Polling Test (Upstream Port Only)

PUT在Polling状态时要能顺利侦测到Hot Reset即为Pass。图(三十)为Gen1的范例,红框中可得知在Polling.Active状态,LVS在收到PUT的TS2之后,发送含有Reset bit的TS2,PUT收到后也回送16个含有Reset bit的TS2,接着LVS再发送连续4个不含Reset bit的TS2,沟通进入U0且要维持50ms。

图(三十)

TD7.28 Hot Reset Detection in U0 Test (Upstream Port Only)

此测项要测试PUT在U0能顺利侦测到Hot Reset且不做Port Configuration沟通即为Pass。图(三十一)为Gen1的范例,从图中红框上到下可知在U0时,LVS发送TS1使状态进入Recovery,接着LVS收到PUT的TS1之后开始发送含有Reset bit的TS2,然后PUT回传16个含有Reset bit的TS2,LVS发送连续4个不含Reset bit的TS2并进入U0维持50ms。

图(三十一)

TD7.29 Hot Reset Initiation in U0 Test (Downstream Port Only)

测试PUT在U0收到Hot Reset能够再训练回U0并维持50ms即为Pass。图(三十二)为Gen1的范例,从图中红框知PUT发送16个含有Reset bit的TS2之后,LVS也会回传含有Reset bit的TS2,接着在连续发送2个不含Reset bit的TS2,训练进入U0并维持50ms。

图(三十二)

TD7.30 Recovery on three consecutive failed RX Header Packets Test

测试PUT在收到连续3个无效的Header Packets要进入Recovery即为Pass。图(三十三)为Gen1的范例,图中前三个红框为LVS发送三次含有无效CRC-5的Header Packet,PUT在前两次收到无效的Header Packet会回送LBAD,LVS会回传LRTY重新发送一次,第三次LVS发送无效Header Packet时,PUT会使状态进入Recovery,重新训练进U0维持50ms代表Pass。

图(三十三)

TD7.31 Hot Reset Failure Test (Downstream Port Only)

测试PUT在做Hot Reset失败时,会做Warm Reset即为Pass。图(三十四)为Gen1的范例,图中可看见第1个红框PUT利用USB30CV发送TS1准备进入Recovery,LVS不回应PUT,在第二个红框可看见PUT进入Rx.Detect发送Warm Reset LFPS。重新从Polling.LFPS沟通进入U0维持50ms。

图(三十四)

TD7.32 Warm Reset Rx.Detect Timeout Test (Hub Downstream Port Only)

此测项已在Link Layer测试中被删除,在TD10.109已包含此测试内容。

TD7.33 Exit Compliance Mode Test (Upstream Port Only)

测试PUT在Compliance Mode收到Warm Reset LFPS能离开Compliance Mode即为Pass。图(三十五)为Gen2的范例,第1个红框代表PUT在Compliance Mode,第二个红框LVS发送Warm Reset LFPS并进入Rx.Detect重新回到Polling.LFPS开始训练。训练进入U0并维持50ms代表Pass。

图(三十六)

TD7.35 Exit U3 by Reset Test (Downstream Port Only)

测试PUT在U3发送Warm Reset LFPS能离开U3即为Pass。图(三十七)为Gen1的范例,从红框上到下顺序,首先PUT利用USB30CV发送LGO_U3,接着LVS回送LAU及PUT回传LPMA进入U3,之后再利用USB30CV使PUT发送Warm Reset LFPS并进入Rx.Detect重新回到Polling.LFPS开始训练。训练进入U0并维持50ms代表Pass。

图(三十七)

TD7.36 Exit U3 Test (Host Downstream Port Only)

测试PUT在U3发送U3 Exit LFPS能离开U3即为Pass,此测项只有Host Silicon需要测试。图(三十八)为Gen1的范例,依红框顺序可知Host进入Sleep状态,PUT发送LGO_U3,LVS回送LAU及PUT的LPMA使状态进入U3。接着叫醒Host,PUT发送U3 Exit LFPS并进入Recovery。重新沟通回U0并维持50ms代表Pass。

图(三十八)

TD7.37 Packet Pending Test (Upstream Port Only)

测试PUT在Control Transfer结束前有释出Packet Pending flag即为Pass。PP bit = 0为Not Pending,PP bit = 1为Pending。图(三十九)为Gen1的范例,在后面一组的Control Transfer中SETUP packet和IN stage中LVS发送含有PP bit为1的封包,接着在STATUS packet发送PP bit为0的封包,然后收到PUT的ACK TP,LVS发送LGO_U1,PUT与LVS回送LAU与LPMA进入U1代表Pass。

图(三十九)

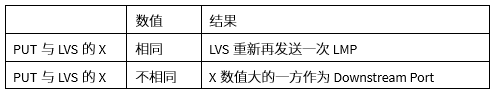

TD7.38 Port Capability Tiebreaker Test

测试PUT与DRD连接能够顺利沟通进入U0维持50ms即为Pass。图(四十)为Gen1的Downstream Port范例,依照红框顺序为PUT发送LMP与LVS沟通,LVS回送一个有Upstream和Downstream Port两种能力的LMP,PUT仍然顺利沟通进入U0且要维持50ms。

图(四十)

倘若今天PUT是一个DRD,设LVS收到LMP的Tiebreaker的数值为X,LVS每收到一次Tiebreaker计数器加1次。计数器只能到5次,超过5次即为失败,沟通状况整理如表(十八),也是要能够顺利进入U0并维持50ms为Pass。

表(十八)

TD7.39 PortMatch Retry Test (Gen 2 Only)

测试PUT在tPollingActiveTimeout之后要重新回到Polling.PortMatch,然后再沟通进入U0维持50ms即为Pass。图(四十一)为Upstream Port撷取部分测试范例,一开始PUT与LVS会用Gen2沟通进入Polling.RxEQ如图中红框,LVS在tPollingActiveTimeout超时前都不回TS1,之后如第二及三个红框重新回到Polling.PortMatch用Gen1沟通进入U0维持50ms。

图(四十一)

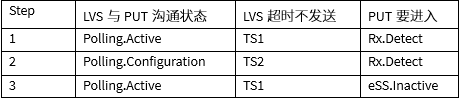

TD7.40 Polling Retry Test (Downstream Port Only)

此测项为确保PUT在tPollingLFPSTimeout之后,前两次能回到Rx.Detect重新从Polling.LFPS沟通,第三次超时之后会进入eSS.Inactive即为Pass。图(四十二)为Gen1部分范例,LVS一开始Termination起来之后不再发任何讯息,PUT在第二个红框进入Rx.Detect。

图(四十二)

若今天PUT为Gen1时,还需继续多测几个步骤。首先LVS断开Termination 200ms再开启Termination,接着测试三个步骤如表(十九):

表(十九)

TD7.41 SetAddress TPF Bit Test (Gen 2 Upstream Port Only)

测试PUT在SetAddress Control Transfer的后部分有将TPF bit设置为1即为Pass。图(四十三)为范例,可从图中底部的红框得知PUT有将TPF bit设置为1代表此测试为Pass。

图(四十三)

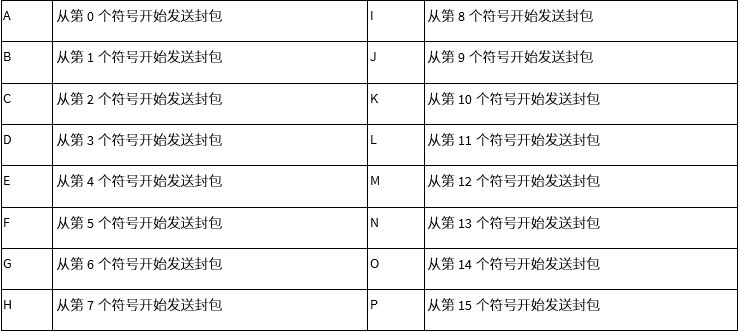

TD7.42 Symbol to Block Alignment Test (Gen 2 Only)

测试PUT每次从不同位置的符号开始发送封包皆能够沟通进入U0并维持50ms即为Pass。Gen2中一个Block有16个符号加上前面的4个Block Header组成。所以测试组合共有16组如表(二十):

参考文献:

- Universal Serial Bus 3.2 Specification, September 22, 2017Universal Serial Bus 3.1 Link Layer Test Specification, Revision 0.95, February 1, 2019

作者

GRL测试工程师 曾威华Wing Tseng

擅长USB、PCIe、SATA接口测试。GRL技术文章作者及讲师。希望帮助大家顺利测试拿到接口Logo,彼此互相交流共同成长飞翔。

本文件中规格特性及其說明若有修改恕不另行通知。

发布日期 2019/06/17 AN-190601-TW