Granite River Labs, GRL

曾威华 Wing Tseng

本篇文章我们将介绍USB3.2的物理层(Physical Layer)测试。在物理层测试当中,分为传送(Transmitter)测试以及接收(Receiver)测试两大部分,传送测试可比喻成验证USB产品的说话能力,接收测试则比喻为USB产品的听力。通过测试认证的USB产品就应当有着稳定的讯号传送及接收能力。USB3.2在开始传输信息之前,会先使用LFPS讯号先行沟通,这种低频周期讯号可节省产品功耗,所以在物理层的讯号测试也会对LFPS讯号进行测试。

USB3.2传送测试 (Tx Test)

-LFPS 发送测试

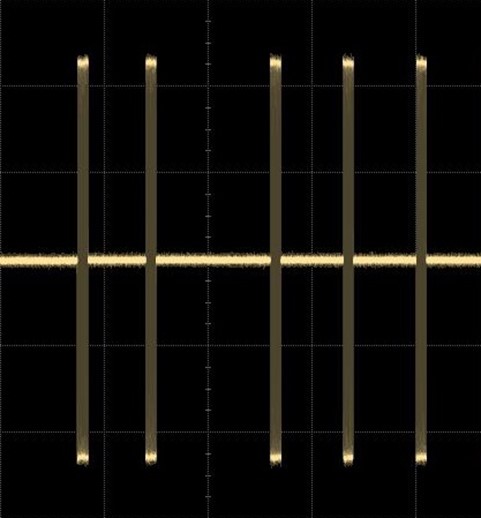

在USB3.2物理层CTS (Compliance Test Specification)中,规定使用待测物(DUT)前五个发送的LFPS Bursts来做测试,图(一)为SCD1在示波器上的波型

图(一)

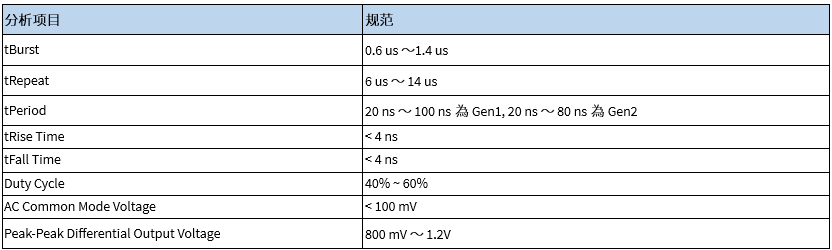

接着将利用撷取到的LFPS波型来分析测试,分析项目和规范如下表(一)

由规范可发现测试对LFPS的Burst相关时间长度及上升、下降时间和占空比(Duty Cycle)有所要求,另外在AC Common Mode Voltage和Peak-Peak Differential Output Voltage对于差分讯号相加或相减之后的规范,代表两个差分讯号的相位差及电压大小不可相差太多。

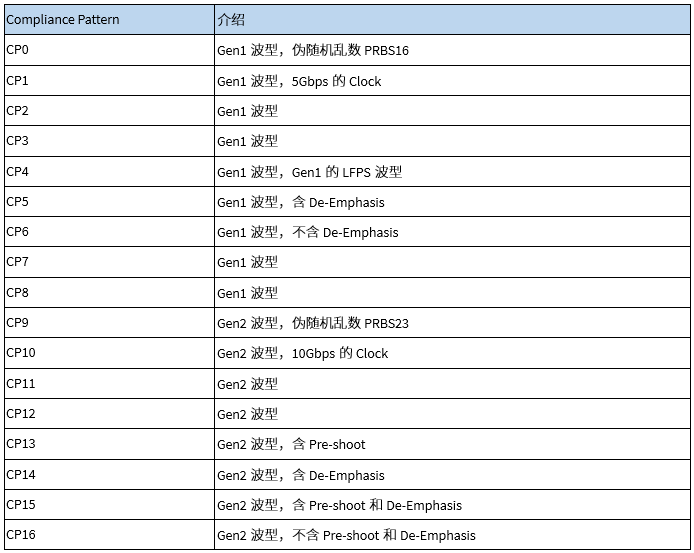

USB3.2 Gen1及Gen2传送测试

在此测试中需要将待测物(DUT)进入Compliance Mode,此模式共有17种Pattern,整理介绍如下表(二)

表(二)

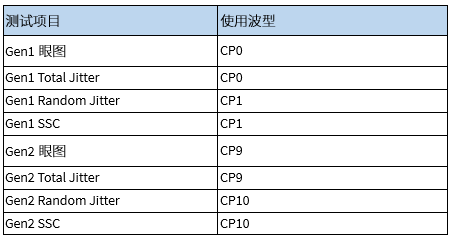

接着我也将测试项目还有其对应的测试波型整理如表(三):

表(三)

眼图测试代表讯号的基本质量,每一个Unit Interval都不压到Eye mask表示发送的讯号能准确的区分逻辑0和逻辑1,电压大小及抖动量也都有在一定的规范内。眼图的规范范围如表(四):

表(四)

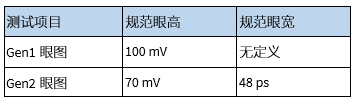

附上USB3.2 Gen2的Long Channel眼图如图(二)供大家参考:

图(二)

Gen2的Tx EQ测试代表了USB芯片发送讯号的EQ调整量要在规范范围表(五)之内

表(五)

SSC测试,在目前越来越高速传输的接口会产生电磁干扰(EMI),USB-IF协会使用了展频频率SSC (Spread Spectrum Clock)的方式来降低传输讯号在同一个频率上的频谱振幅,也进而减少了电磁干扰。SSC的原理类似我们的频率调变(Frequency Modulation),对传输讯号做一个三角波周期的频率调变。图(三)为Normal Mode SSC三角波周期调变范围。

图(三)

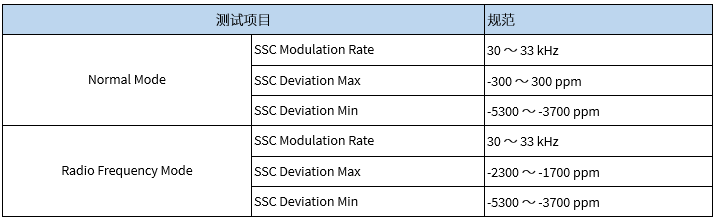

表(六)为SSC测试项目及其规范:

表(六)

USB3.2接收测试 (Rx Test)

-LFPS接收测试

此测试只针对USB3.2 Gen1的讯号做测试,测试目的是希望待测物能够正确的接收到Link Partner的LFPS。测试原理仪器端会发送四种较差的LFPS给待测物,若待测物接收到这四种LFPS还能够顺利沟通并回传TSEQ则代表通过此测试。表(七)为测试使用的四种LFPS:

表(七)

USB3.2 Gen1及Gen2接收测试

在接收测试中,要使待测物进入Loopback Mode。在此模式时,USB产品会回传收到的讯号。测试目的为USB产品在接收讯号上能够准确判断Link Partner在传送的讯号。所以测试上仪器会先与待测物沟通进入Loopback Mode,接着开始发送测试讯号,当中测试讯号会加上一定的抖动频率及其对应的抖动量给待测物,待测物接收到测试讯号后回传给误码仪(Error Detector),只要小于等于1个Bit Error,表示待测物通过Rx测试。

USB3.2 Gen1共有8个Sj测试点,每点测试3×1010个Bits,每点测试时间约为6秒钟,测试点如表(八):

表(八)

USB3.2 Gen2共有9个Sj测试点,每点测试约1.2×1012个Bits,每点测试时间约为2分钟,测试点如表(九):

表(九)

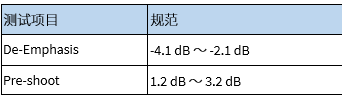

再附上USB3.2 Gen2接收测试的结果如图(四)供大家参考:

图(四)

参考文献:

- Universal Serial Bus 3.2 Specification, September 22, 2017

- Electrical Compliance Test Specification Enhanced SuperSpeed Universal Serial Bus, February 14, 2017

作者

GRL测试工程师曾威华Wing Tseng 擅长USB、PCIe、SATA接口测试。GRL技术文章作者及讲师。希望帮助大家顺利测试拿到接口Logo,彼此互相交流共同成长飞翔。

本文件中规格特性及其說明若有修改恕不另行通知。

发布日期 2019/05/20 AN-190503-TW