Granite River Labs, GRL

曾威华 Wing Tseng

随着3C产品的传输接口与时俱进,例如:USB、Thunderbolt、Ethernet…,在主板上的PCIe也必须跟着提升速度,目前PCI-SIG已公开PCIe速度有Gen1〜Gen5五种传输速度。

参考时钟(Reference Clock)

一个标准PCIe装置的参考时钟有正负两个差分讯号,规格整理如表(一):

表(一)

编码方式

PCIe所使用到的编码方式也整理如表(二):

表(二)

所以可发现PCIe 3.0 和PCIe 4.0比起PCIe 1.1和2.0更有效率的传输数据。PCIe 3.0与PCIe 4.0的编码有效率98.46%而PCIe 1.1与PCIe 2.0只有80%。

发送端Equalization (Tx EQ)

在PCIe的传送中使用到EQ来优化讯号,以下我将分别针对PCIe 1.1、2.0、3.0和4.0整理相对应的EQ值。首先是PCIe 1.1和2.0如表(三):

表(三)

随着PCIe 2.0传输速度的提升,比PCIe 1.1多增加了De-Emphasis -6.0dB的EQ。

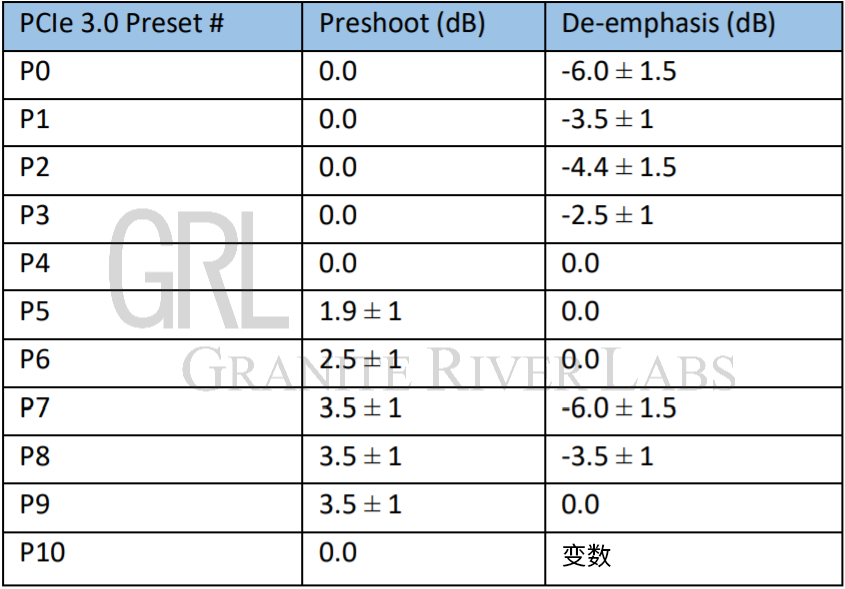

接着整理出PCIe 3.0与PCIe 4.0的Preset表(四):

表(四)

P10的De-emphasis为变量,当传送端的Boost level为Full Swing时使用此组Preset,在PCIe 4.0中P11〜P15目前保留尚未定义Pattern。

接收端Equalization (Rx EQ)

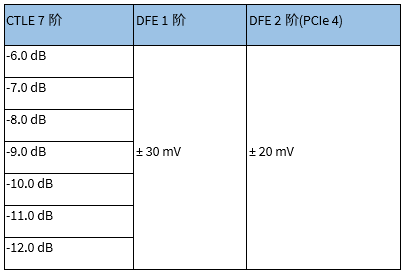

在PCIe 1.1及2.0中并没有使用Rx EQ,但到了PCIe 3.0则开始使用Rx EQ来优化讯号,我也将PCIe 3.0与PCIe 4.0的Rx EQ整理如表(五), PCIe 4.0比起PCIe 3.0的Rx EQ多了DFE的第二阶修正:

表(五)

动态Equalization

在PCIe 3.0与PCIe 4.0中Root Complex(RC)和Adding In Card(AIC)会使用动态EQ来互相找到极佳配置的Tx和Rx EQ参数,在PCIe 3.0的动态EQ分有以下四个步骤整理如表(六) , 若RC和AIC双方皆有支持PCI-e 4.0,当做完PCI-e 3.0的动态EQ之后,接着就会开始做PCI-e 4.0的动态EQ:

表(六)

参考文献:

- PCI Express Base Specification Revision 3.1a, December 7, 2015

- PCI Express Card Electromechanical Specification Revision 3.0, July 21, 2013

- PCI Express Base Specification Revision 4.0 Version 1.0, September 27, 2017

- PCI Express Card Electromechanical Specification Revision 4.0 Version 0.9, November 27, 2018

作者

GRL测试工程师 曾威华Wing Tseng 擅长USB、PCIe、SATA接口测试。GRL技术文章作者及讲师。希望帮助大家顺利测试拿到接口Logo,彼此互相交流共同成长飞翔。

本文件中规格特性及其說明若有修改恕不另行通知。

发布日期 2019/07/30 AN-190703-TW