Granite River Labs, Cyan Chen 陈昀

USB4信号完整性要求对 PCB Layout 设计的影响

在高速传输总线设计中,验证和解决信号完整性问题宜早不宜迟。初始阶段,PCB 设计人员和硬件工程师会将电路级的原理图转换为 PCB Layout。同时,信号完整性 (SI) 工程师将对硬件设计进行信号完整性分析,并提供反馈或建议以优化信号。而 PCB Layout 在这一过程中往往需要进行修改。

由于 USB4 具有更高的数据传输速率、更强的功能以及向下兼容性的要求,设计也因而更加复杂。为了避免昂贵的 PCB 设计返工和产品上市延迟,硬件工程师往往需要在硬件设计过程的同时实时验证信号完整性,而不是仅仅依靠 SI 工程师在设计完成后进行验证。

本文将针对这一独特难题,介绍如何根据 USB4 最新规范验证 PCB 设计的信号完整性,以帮助设计团队实现更高的设计效率。

USB4 v2 信号模式及其电气要求

根据 USB-IF 于 2022 年 10 月发布的公告,最新版本的 USB4 v2规范使 USB Type-C 的性能达到了 80 Gbps。该规范引入了 3 级脉冲幅度调制(PAM3)的 Gen 4 运行模式,以全新的物理层架构实现更高数据传输速率,通过现有的 40Gbps USB Type-C 无源电缆和新定义的 80Gbps USB Type-C 有源电缆进行传输,提高了对印刷电路板(PCB)设计中 USB4 信道的信号完整性(SI)要求。

阻抗要求

在 USB4规范的要求中,USB4高速差分线对建议的受控阻抗为 80-85Ω,单端参考阻抗为42.5Ω。因而测量 USB4信道的信号完整性所使用的测量夹具,也被要求以42.5Ω单端参考阻抗为目标设计。

一般来说,在 PCB 走线中差分阻抗的线路形状(线宽和线距)决定了能否实现80 -85 Ω差分阻抗的标准。对于较短的互连器件(1-3 英寸),阻抗控制至关重要。而较长的通道(5-10 英寸)的主要设计考虑为走线损耗和衰减则。

如果您正在设计一条长距离的通道,那么您的主要设计目标就是减少损耗/衰减。假设通道长度是固定的,在单端通道中,降低损耗意味着在较厚的基板上设计导线,从而以较宽的走线宽度实现相同的受控阻抗。更宽的线宽可降低单位长度走线的电阻,从而减少总损耗。

与单端情况一样,更宽的线宽也能降低差分通道的总损耗。在基板厚度固定的情况下,有两个参数可以影响差分阻抗:线宽和线距。以一对相隔一倍线宽且差分阻抗为Zdiff = 85 Ω的差分线对为例,如果增加线宽但保持间距不变,差分阻抗将低于原始阻抗。因此,需要同时增加线对之间的间距,以补偿降低的差分阻抗。随着归一化间距(间距除以导线宽度)的增加,导线宽度也必须增加,以保持相同的差分阻抗从而减少总损耗。大于一的归一化间距是保持差分阻抗同时降低损耗的良好经验法则。而在通道设计中尽量减少线路的穿层、过孔以及线路经过的元器件数量,也能帮助减少由于阻抗反射带来的衰减。

回波损耗

由于采用了基于 PAM3的新物理层架构,与传统的 2 级信令NRZ 相比,PAM3 信令方案在同一电压范围内创建了三个不同的电压电平,因此Gen4发送端和接收端通道需要满足与 Gen 2 和 Gen 3 模式下不同的回波损耗要求。

在最新的USB4 v2规范中,Gen2和Gen2模式下定义了差分回波损耗和共模回波损耗两个参数。而Gen4模式下规范给出的是差分回波损耗和更为严格的集成回波损耗(IRL, Integrated Return-Loss)两个参数规格。

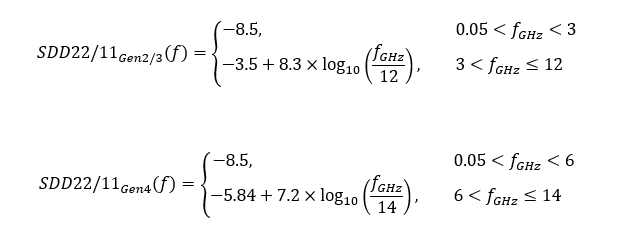

发送端和接收端的差分回波损耗要求如下公式所示:

根据上述公式可以绘制出Gen2/Gen3/Gen4模式下的差分回波损耗的模版,如下图所示:

图1:USB4差分回波损耗模板

我们可以直观的看出,在 Gen4模式下对回波损耗的要求更加严格。 Gen 2 和 Gen 3 模式要求在 3 GHz以下频段满足 -8.5 dB的回波损耗,而 Gen4则延伸频段,要求在6 GHz以内,都要小于-8.5dB的回波损耗。同时,Gen4模式下回波损耗需要关注的频段也从 Gen2和 Gen3模式要求的12 GHz提高到了14GHz。回波损耗在Gen4的高频段要求更严格(如图一)。比较不同模式之间可接受的差分回波损耗,可以发现从 6 GHz 到 14GHz 时,Gen4允许回波损耗从 -8.5 dB 增加到最大 -5.84 dB,仅增加了 2.66 dB;而 Gen2或 Gen3允许增加 5 dB,这意味着 Gen4对通道阻抗匹配的要求变得更高。与通道受控阻抗不同的短阻抗线长度会导致回波损耗随着频率的增加而增加。Gen4回波损耗要求的 2.66 dB 差分回波损耗增幅较小,这表明需要在走线设计中更加注意保持通道中受控阻抗的一致性,在电容与ESD器件的选择上,也同时要注意元件尺寸与回波损耗特性。

此外,共模回波损耗也是衡量传输线电磁兼容性能的重要指标之一,较高的共模回波损耗可有效减少由于传输线带来的干扰和噪声。在Gen2和Gen3模式下,共模回波损耗要求如下公式所示:

图2:共模回波损耗模板

对于自带线缆的USB4终端设备,由于其线缆的不可分割性而导致量测点不同,其共模回波损耗要求相对降低:

IRL(Integrated Return Loss)

在 USB4 V2.0的规范中,为了支持将比特率提高到 80 Gb/s而带来的额外的信号完整性要求,USB-IF 引入了集成回波损耗IRL(Integrated Return Loss) 要求,利用入射信号的集成功率谱密度对反射信号的集成功率谱密度进行归一化处理以算出发射器的集成回波损耗。其中,接收端 IRL 的要求则为RX_IRL≤-14.5dB,发射端IRL的要求如下公式所示:

其对应的模板如下图所示。

图3:USB4 Gen4发送端IRL最大限制范围模板

其中TX_ISI_MARGIN是通过测量所得的发送端码间干扰(ISI)的裕量值。该裕量对应于发射机信号与残余 ISI 的比率。

USB4阻抗及回波损耗的测量

由于正式的USB4 v2测试规范尚未发布,因此我们借由目前已经发布并使用的USB4 Gen2/3 模式测试规范,来给大家介绍一下阻抗及回波损耗的测量。

如前文所述,USB4高速差分线对建议的受控阻抗为 80-85Ω,单端参考阻抗为42.5Ω。因而测量USB4信道的信号完整性所使用的测量夹具,也被要求以42.5Ω单端参考阻抗为目标设计。而我们在测量通道阻抗及回波损耗时,传统的网络分析仪的端口阻抗是50 Ω,因此一个关键的步骤,则是应该将其转化为 42.5 Ω 的单端口阻抗以实施实际的测量。

我们在测量USB4信号通道的阻抗及回波损耗时,使用如下图所示的测试环境:

图4:USB4阻抗及回波损耗测试连接图

在 USB4 的Gen2、Gen3模式下,我们在阻抗和回波损耗的实际测试中,通过USB4控制器与待测物沟通,让待测物端口发送PRBS31码型,用矢量网络分析仪测量对应的阻抗及回波损耗参数并得到结果。

在Gen4模式下,由于采用的是PAM3信号模式,则需要待测物发送PRTS7码型以执行测量,同时,借由USB4 v2 Sigtest工具强大的计算能力,根据网络分析仪测得的S参数文件以计算得出所需的回波损耗结果。而对于集成回波损耗,则会同时需要调用对应的时序及电压测量波形文件,来计算码间干扰TX_ISI_MARGIN,以验证发送端IRL的结果是否符合要求。

借助专业工程师,实现更高效的 USB4 信号完整性设计

与 GRL 携手,优化您的 USB4产品制造流程。作为 GRL 是 USB-IF 授权的独立认证测试实验室(ITL),USB 专家团队可提供深厚的 USB 专业知识,以最省时、最具成本效益的方式让您更接近 USB 生态系。欢迎联系我们,进行个性化的生产流程评估,并获得有关测试服务和解决方案的推荐。

参考文档

Universal Serial Bus 4 (USB4®) Specification, Version 2.0 with Errata and ECN through June 29, 2023

Universal Serial Bus 4 (USB4™) Router Assembly Electrical Compliance Test Specification,Revision 1.03, June 8, 2022

Universal Serial Bus 4 (USB Type-C) Captive Device Electrical Compliance Test Specification,Revision 1.02,June8, 2022